Volume 28, No.1 Pages 6 - 11

1. 最近の研究から/FROM LATEST RESEARCH

オペランドX線トポグラフィー法を用いた動作中SiC MOSFETにおける積層欠陥拡張の観察

Observation of Stacking Fault Expansion Motions in Operating SiC MOSFETs Using In-operando X-ray Topography Analysis

[1](株)日立製作所 研究開発グループ Research and Development Group, Hitachi, Ltd.、[2]九州シンクロトロン光研究センター ビームライングループ Beamline Group, SAGA Light Source

- Abstract

- カーボンニュートラルの実現に向けて、高効率なパワーエレクトロニクス機器の利用拡大がより重要となる。現在、パワーデバイスの材料にはSiが広く使われているが、更なる省エネルギー化に向けてSiCを使ったパワーデバイスの実用化が開始されている。SiCパワーデバイスは、高耐圧・大電流が求められる電力やモビリティ分野での活躍が特に期待されているが、SiCに含まれる結晶欠陥がその普及を妨げている。具体的には、SiC MOSFETでは、デバイスの動作中に積層欠陥が拡張することで、抵抗が増加する信頼性の問題が課題となる。この課題を解決するために、オペランドX線トポグラフィー法を開発し、世界で初めて動作中SiC MOSFETにおける積層欠陥の拡張を直接観察することに成功した。加えて、デバイスの実動作条件下での積層欠陥の拡張機構を解明することで、高信頼なSiC MOSFETの実現に大きく貢献した。

1. SiCパワーデバイスの特長と課題

カーボンニュートラルの実現に向けて、電力の供給・需要側の双方で省エネルギー化・電動化が推進されている。電力の供給から消費の末端までを支えるパワーエレクトロニクス機器は、電力の変換や制御を効率よく実施することで、社会を支えるキーコンポーネントとして活躍している。電気エネルギーへの依存度が高まる社会背景の中で、パワーエレクトロニクス機器を用いた電気エネルギーの有効活用がより一層重要となり、パワーエレクトロニクス機器による更なる省エネルギー化が期待される。

パワーエレクトロニクス機器で使用される半導体デバイスはパワーデバイスと呼ばれる。パワーデバイスの特性は、使用する材料に大きく影響を受ける。パワーデバイスの材料として、これまで長年にわたってSiが使用されてきたが、更なる省エネルギー化に向けてSiCを使ったパワーデバイスの実用化が開始され、市場が成長している[1-3][1] J. A. Cooper, Jr. and A. Agarwal: Proc. IEEE 90 (2002) 956.

[2] H. Okumura: Jpn. J. Appl. Phys. 45 (2006) 7565.

[3] T. Kimoto: Jpn. J. Appl. Phys. 54 (2015) 040103.。SiCはSiに比べて大きなバンドギャップと優れた熱安定性を持つため、SiCパワーデバイスは高耐圧かつ低損失で、高温でも動作可能な優れた特長を有する。これらの特長から、SiCパワーデバイスは高耐圧・大電流が求められる電力やモビリティ分野での活躍が特に期待されている。しかし、材料であるSiCには結晶欠陥が多いという最大の欠点がデバイスの高信頼化や普及の妨げとなっている。

2. SiC MOSFETにおけるバイポーラ劣化現象

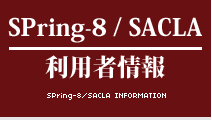

現在最も応用範囲が広いSiCパワーデバイスは、SiC MOSFETであり、その単位セルの断面概略図を図1(a)に示す。SiC MOSFETはSiC基板上にSiCエピタキシャル層を成膜したSiCエピタキシャル基板上に作成され、ゲート電極・ソース電極・ドレイン電極の3つの端子を持つ。チップの中には、図1(a)で示す単位セルが敷き詰められ、SiCエピタキシャル基板の表面側は複雑な立体構造が形成されている。

図1 (a) SiC MOSFETの断面概略図(単位セル)、(b) バイポーラ劣化前後の電気特性。

SiC MOSFETを用いたパワーモジュールでは、MOSFETの内蔵PNダイオード(図1(a)内に図示する)を還流ダイオードとして活用することで小型・低コストなダイオードレス構造が実現可能であるが、内蔵PNダイオードの動作中にデバイスのオン抵抗が徐々に増加するバイポーラ劣化現象が課題となる。これは、SiCに存在する線状の結晶欠陥である基底面転位(BPD: Basal Plane Dislocation)が、電子-正孔再結合エネルギーを受け取り、面状の積層欠陥に拡張することで起こる[4-5][4] M. Skowronski and S. Ha: J. Appl. Phys. 99 (2006) 011101.

[5] T. Kimoto and H. Watanabe: Appl. Phys. Express 13 (2020) 120101.。積層欠陥は、電流の流れを阻害する高抵抗層であるため、動作中に徐々にデバイスの抵抗が増加してしまう。図1(b)にはSiC MOSFETのバイポーラ劣化現象の例として、内蔵PNダイオードを充分な時間動作させ、前後の電気特性を比較した結果を示す。内蔵PNダイオードの動作中に積層欠陥が拡張することで、動作前に比べて電流が流れにくくなり、抵抗が増加している。

SiC MOSFETにおけるバイポーラ劣化現象を解明するためには、動作中SiC MOSFET内部の結晶欠陥の挙動を観察する必要があるが、デバイス構造が非常に複雑であるため、通常の試験環境では観察が困難であった。そこで、動作中SiC MOSFETにおける結晶欠陥の挙動を可視化するために、オペランドX線トポグラフィー法を開発した[6][6] K. Konishi, R. Fujita, K. Kobayashi, A. Yoneyama, K. Ishiji, H. Okino, A. Shima and T. Ujihara: J. Appl. Phys. 130 (2021) 145703.。加えて、本手法で得られた結果を解析することで、デバイスの実動作条件下での積層欠陥の拡張機構を解明し、高信頼なSiC MOSFETの実現を目指した。

3. オペランドX線トポグラフィー法

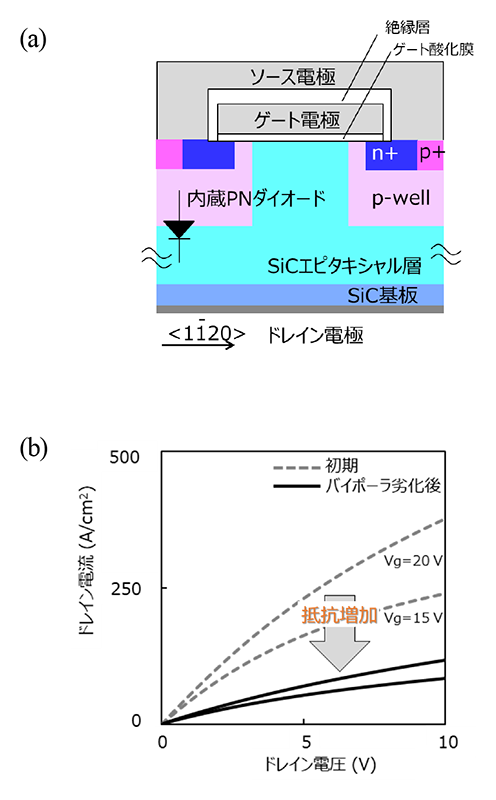

図2にオペランドX線トポグラフィー評価系を示す。評価系は、X線カメラ、2θアーム、ゴニオメーター、サンプルホルダー、サンプル冷却機構、電流ストレス印加用電源ユニットから構成されている。検出器には従来のX線フィルムに替えて高精細かつ高速なX線カメラを採用することで、X線トポグラフィー像の連続撮像を可能とした。X線トポグラフィー像は、デジタルデータとして得られるので、画像処理技術を利用してSiC MOSFET内部の積層欠陥の変化を解析した。また、X線トポグラフィー評価は、Si(111)単色器で10 keVに単色化した放射光を用いて反射配置で実施した。回折面は、積層欠陥が観察できるSiC(022 10)を選定した。

図2 開発したオペランドX線トポグラフィー評価系。

SiC MOSFETに電流を流すため、SiC MOSFETをDBC(Direct Bonded Copper)基板上に半田を用いて実装した。その後、SiC MOSFET表面に形成されたゲート、ソース電極上にワイヤを接合し、DBC基板を電流ストレス印加用電源ユニットと配線ケーブルで接続した。オペランドX線トポグラフィー観察時には、SiC MOSFET内蔵PNダイオードに流す電流を任意に変更可能である。また、DBC基板は冷却機構と接続されたヒートシンク上に設置されており、動作中のMOSFETの接合温度も任意に制御できる。

SiC MOSFETに電流を流し始めると、SiC MOSFETの接合温度が上昇する。この通電による発熱の影響のため、SiC MOSFETのブラッグ回折条件を満たすX線の入射角がドリフトし、回折したX線強度が不安定になる。この不安定性を抑制するため、SiC MOSFETの動作中にブラッグ回折条件を満たす入射角を維持するように設計されたフィードバック機構を導入した[7][7] A. Yoneyama, S. Takeya, T. T. Lwin, D. Takamatsu, R. Baba, K. Konishi, R. Fujita, K. Kobayashi, A. Shima, M. Kawamoto, H. Setoyama, K. Ishiji and Y. Seno: J. Synchrotron Rad. 28 (2021) 1966-1977.。本フィードバック機構では、取得したX線トポグラフィー像の強度分布が均一となるような角度を制御PCで計算し、ステージの角度、すなわちX線入射角の補正を自動で行った。

4. 動作中SiC MOSFET内での積層欠陥拡張の様子

SiC MOSFETの内蔵PNダイオードに電流を流しながら、オペランドX線トポグラフィー観察を行い、その結果を解析した。

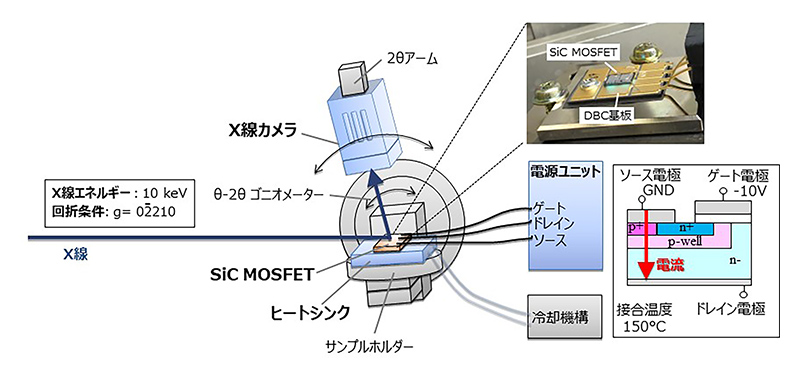

図3(a)はSiC MOSFETの内蔵PNダイオードに電流を流した際のタイムチャートと通電条件である。ゲート電圧は-10 V、接合温度は150°Cに設定した。通電試験は、段階的に電流を増やした3ステップとし、電流密度は70 A/cm2, 220 A/cm2, 400 A/cm2と設定した。通電時間は、各電流密度でそれぞれ2.5時間, 20分, 20分とした。また、X線カメラの露光時間は1秒とした。本解析で使用したタイミングを図3(a)において、タイミング1, 2,…6として示した。

図3 (a) SiC MOSFETの内蔵PNダイオードに対して実施した通電試験条件とタイムチャート、(b)-(g) X線トポグラフィー像、(b) 通電試験前の状態、(c)-(g) タイミング1と2、タイミング2と3、タイミング3と4、タイミング4と5、タイミング5と6の間に拡張した積層欠陥。

各タイミングで得られたX線トポグラフィー像を減算処理することで、特定のタイミング間に拡張した積層欠陥を抽出した。画像処理後のX線トポグラフィー像を図3(c)-(g)に示す。図3(b)はタイミング1(通電試験前)のX線トポグラフィー像である。図3(b)から、通電試験前のSiC MOSFET内には積層欠陥がないことが確認できる。しかし、図3(c)に示すように、70 A/cm2の通電試験の間にいくつかの積層欠陥が拡張した。図3(d)に示すように、220 A/cm2の通電試験開始時には、70 A/cm2の通電試験で拡張した積層欠陥とは別に、新たな積層欠陥が拡張した。図3(e)では、220 A/cm2の通電試験で遅れて拡張した積層欠陥が確認できる。同様に、図3(f)に示すように、400 A/cm2の通電試験開始時には、70 A/cm2や220 A/cm2の通電試験で拡張した積層欠陥とは別に、新たな積層欠陥が拡張した。また、図3(g)では、400 A/cm2の通電試験で遅れて拡張した積層欠陥が確認できる。

これらの結果から、積層欠陥が拡張する様子が鮮明に観察され、世界で初めて動作中SiC MOSFETにおける積層欠陥の拡張を直接観察することに成功した。また、積層欠陥はそれぞれ異なる電流密度で拡張を開始すること、拡張開始タイミングは同じ電流密度でも異なることが明らかになった。

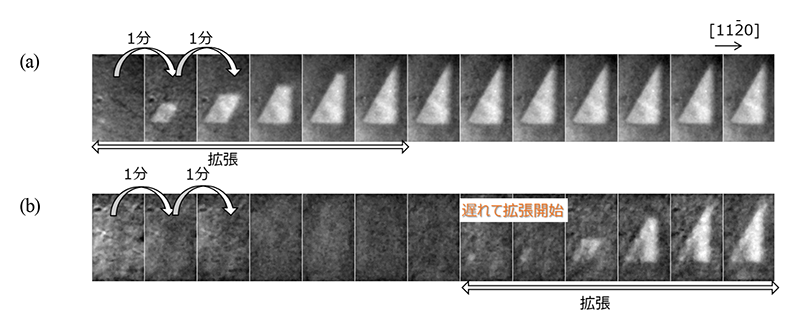

図4は、SiC MOSFETにおける積層欠陥の拡張の様子を1分間隔で示した時間分解X線トポグラフィー像である。これらは、内蔵PNダイオードへの電流密度を220 A/cm2に設定して撮像されたものである。図4には、(a)通電開始時に積層欠陥が拡張する標準的な場合、(b)積層欠陥が遅れて拡張開始した場合、の2つの例を示す。図4に示すように、拡張する積層欠陥の形状は、初期のひし形から、台形に変形し、最終的に三角形に変化する。なお、積層欠陥の起点となるBPDはSiC MOSFET表面から深い領域に位置するため、図4の撮像条件では検出されていない。図4(b)から、(a)と同じ電流密度であっても、積層欠陥が遅れて拡張を開始することがわかる。先行研究を考慮すると、同じチップ、同じ電流密度であっても、積層欠陥の起源であるBPDの構造の違いにより、積層欠陥拡張のタイミングが同期しなかったと推察するが[8-9][8] S. Hayashi, T. Yamashita, J. Senzaki, T. Kato, Y. Yonezawa, K. Kojima and H. Okumura: Appl. Phys. Express 12 (2019) 051007.

[9] Y. Ishikawa, M. Sudo, Y. Yao, Y. Sugawara and M. Kato: J. Appl. Phys. 123 (2018) 225101.、それを明らかにするためには、TEM分析やX線トポグラフィー分析によるバーガーズベクトル解析などの詳細な検討が必要である。

図4 SiC MOSFETにおける積層欠陥拡張の様子。(a) 通電試験開始時に積層欠陥が拡張するケース、(b) 積層欠陥が遅れて拡張するケース。

オペランドX線トポグラフィー観察において、動的に得られた観察結果は非常に重要であり、図4(b)に示すような遅れて拡張する場合を考慮に入れて、バイポーラ劣化現象の対策をする必要がある。

5. 積層欠陥の拡張速度と電流密度の関係

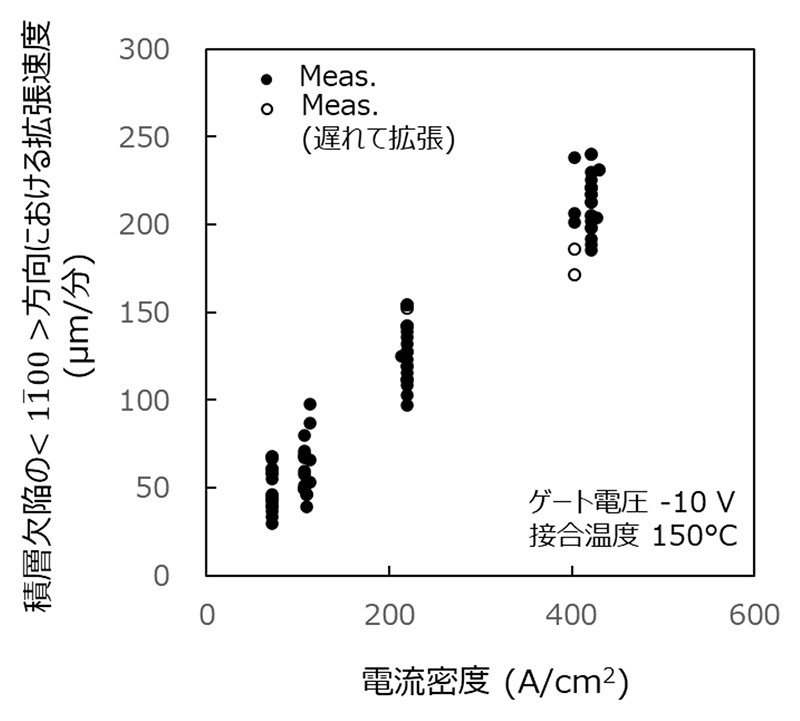

続いて、SiC MOSFET内で拡張する積層欠陥の拡張速度を評価した。なお、この拡張速度は、<1100>方向へ投影した値である。図5は、積層欠陥の<1100>方向の拡張速度を、SiC MOSFET内蔵PNダイオードに流す電流密度の関数として示したものである。図5から、多少のばらつきはあるものの、SiC MOSFET内における<1100>方向の積層欠陥の拡張速度は、内蔵PNダイオードに流れる電流密度に伴って大きくなる。これは、積層欠陥拡張の駆動力となるSiC中の正孔密度が電流密度に伴って大きくなるためである。図4(b)に示した、遅れて拡張を開始した積層欠陥の拡張速度は、標準的な場合とほとんど等しく、その発生頻度は少ないことが明らかになった。

図5 積層欠陥の<1100>方向における拡張速度と電流密度の関係。

6. まとめと今後の展望

SiC MOSFETにおけるバイポーラ劣化現象を解明するために、動作中SiC MOSFETにおける結晶欠陥の挙動を可視化するオペランドX線トポグラフィー法を開発した。

内蔵PNダイオードに対する電流密度を70 A/cm2, 220 A/cm2, 400 A/cm2と段階的に大きくして観察を行った結果、動作中SiC MOSFETにおける積層欠陥の拡張を直接観察することに世界で初めて成功した。加えて、X線トポグラフィー像を解析することで、各電流密度で異なる積層欠陥が拡張すること、同じ電流密度でも拡張開始のタイミングが異なることを明らかにした。また、時間分解X線トポグラフィー像から抽出した積層欠陥の拡張速度は内蔵PNダイオードに流れる電流密度に伴って大きくなった。

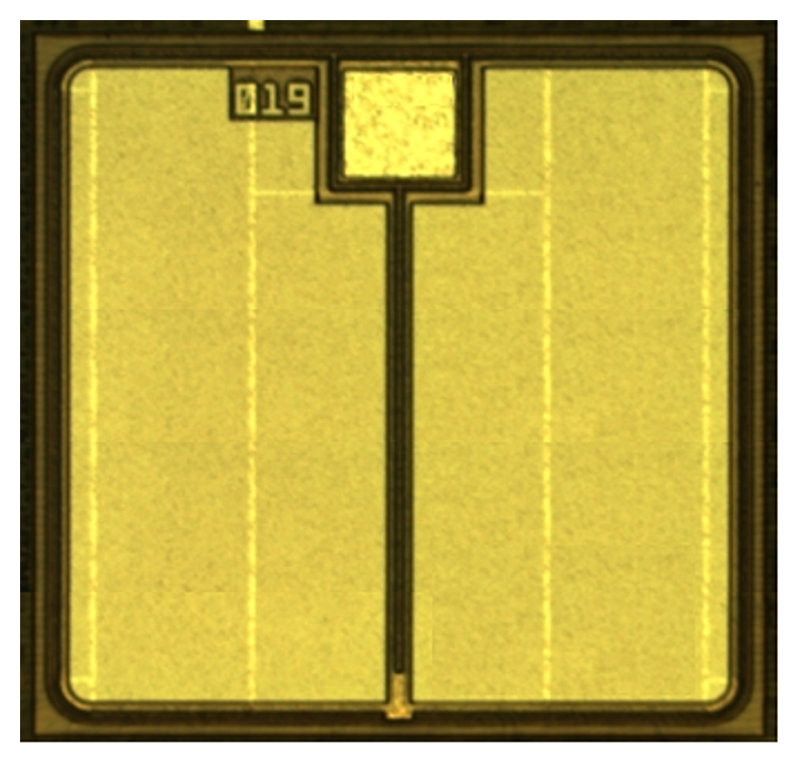

本研究で開発したオペランドX線トポグラフィー法を活用することで、デバイスの実動作条件下での積層欠陥の拡張機構を解明し、図6に示すSiCパワーモジュールのダイオードレス構造を実現する高信頼なSiC MOSFETの実現に貢献した[10][10] 「耐久性と低消費電力特性を両立した新構造SiCパワーデバイス「TED-MOS®」を製品化」株式会社日立製作所、ニュースリリース、2021年1月26日。このSiC MOSFETを用いたSiCパワーモジュールにより、電力・鉄道・電気自動車などの分野で大きな省エネルギー効果が得られ、カーボンニュートラル実現に向けたCO2削減目標達成への貢献が期待される。

図6 SiCパワーモジュールのダイオードレス構造を実現する高信頼SiC MOSFET。

謝辞

本実験はSPring-8のBL16B2ビームライン(課題番号:2018A5400、2018B5400、2019A5400、2019B85400、2020A5400)と、SAGA-LSのBL07、BL09ビームラインにおいて行われました。

参考文献

[1] J. A. Cooper, Jr. and A. Agarwal: Proc. IEEE 90 (2002) 956.

[2] H. Okumura: Jpn. J. Appl. Phys. 45 (2006) 7565.

[3] T. Kimoto: Jpn. J. Appl. Phys. 54 (2015) 040103.

[4] M. Skowronski and S. Ha: J. Appl. Phys. 99 (2006) 011101.

[5] T. Kimoto and H. Watanabe: Appl. Phys. Express 13 (2020) 120101.

[6] K. Konishi, R. Fujita, K. Kobayashi, A. Yoneyama, K. Ishiji, H. Okino, A. Shima and T. Ujihara: J. Appl. Phys. 130 (2021) 145703.

[7] A. Yoneyama, S. Takeya, T. T. Lwin, D. Takamatsu, R. Baba, K. Konishi, R. Fujita, K. Kobayashi, A. Shima, M. Kawamoto, H. Setoyama, K. Ishiji and Y. Seno: J. Synchrotron Rad. 28 (2021) 1966-1977.

[8] S. Hayashi, T. Yamashita, J. Senzaki, T. Kato, Y. Yonezawa, K. Kojima and H. Okumura: Appl. Phys. Express 12 (2019) 051007.

[9] Y. Ishikawa, M. Sudo, Y. Yao, Y. Sugawara and M. Kato: J. Appl. Phys. 123 (2018) 225101.

[10] 「耐久性と低消費電力特性を両立した新構造SiCパワーデバイス「TED-MOS®」を製品化」株式会社日立製作所、ニュースリリース、2021年1月26日

(株)日立製作所 研究開発グループ

〒185-8601 東京都国分寺市東恋ヶ窪1-280

TEL : 042-323-1111

e-mail : kumiko.konishi.qo@hitachi.com

(株)日立製作所 研究開発グループ

〒185-8601 東京都国分寺市東恋ヶ窪1-280

TEL : 042-323-1111

e-mail : ryusei.fujita.kw@hitachi.com

(株)日立製作所 研究開発グループ

〒185-8601 東京都国分寺市東恋ヶ窪1-280

TEL : 042-323-1111

e-mail : keisuke.kobayashi.ay@hitachi.com

(株)日立製作所 研究開発グループ

〒185-8601 東京都国分寺市東恋ヶ窪1-280

TEL : 042-323-1111

e-mail : akio.yoneyama.bu@hitachi.com

九州シンクロトロン光研究センター ビームライングループ

〒841-0005 佐賀県鳥栖市弥生が丘8丁目7番地

TEL : 0942-83-5017

e-mail : yoneyama@saga-ls.jp

九州シンクロトロン光研究センター ビームライングループ

〒841-0005 佐賀県鳥栖市弥生が丘8丁目7番地

TEL : 0942-83-5017

e-mail : ishiji@saga-ls.jp

(株)日立製作所 研究開発グループ

〒185-8601 東京都国分寺市東恋ヶ窪1-280

TEL : 042-323-1111

e-mail : hiroyuki.okino.wj@hitachi.com

(株)日立製作所 研究開発グループ

〒185-8601 東京都国分寺市東恋ヶ窪1-280

TEL : 042-323-1111

e-mail : akio.shima.yw@hitachi.com