Volume7 No.1

SPring-8 Section B: Industrial Application Report

次世代CMOSチャネル実現に向けた硬X線光電子分光によるグラフェン・ゲート絶縁膜界面構造の最適化

Optimization of the Interface between Graphene and Gate Insulator Studied by Hard X-ray Photoelectron Spectroscopy for Future CMOS Channel

a(独)産業技術総合研究所 グリーン・ナノエレクトロニクスセンター, b(株)富士通研究所

aGNC, AIST, bFujitsu Labotarories, Ltd.

- Abstract

-

我々はグラフェンのチャネル材料としての高いポテンシャルに着目し、次世代CMOSチャネル候補として大面積基板上での成長技術やFETトランジスタ作製プロセス開発を行ってきた。今回は、原子層堆積法や蒸着法などの異なる方式で作製した絶縁膜とグラフェンの界面電子状態を硬X線光電子分光により調べることで、現在想定し得るゲート絶縁膜候補材料とグラフェン界面での電子状態から絶縁膜としての適性の検討を行い、グラフェン直上には SiO2 を絶縁膜として堆積することが望ましく、その上に別途High-k等の絶縁膜を堆積すれば良いことが判明した。今後さらなる検討を行いグラフェンFET作製プロセスの最適化を推し進める予定である。

Keywords: 硬X線光電子分光、グラフェン、CMOS

背景と研究目的:

近年、低炭素社会実現に向けた技術開発のニーズは様々な分野において大きくなりつつあり、半導体技術においてもその一環としてさらなる高速化及び低消費電力化が求められている。今日まで、そのような半導体デバイスの性能向上は微細化によって達成されてきたが、微細化による弊害やその限界が指摘されつつあることから、より高速化・低消費電力化が実現可能な代替材料が必要となっている。中でもグラファイト一層分からなるグラフェンは、シリコンと比較して圧倒的に高い電子移動度や高い熱伝導性から次世代のチャネル材料・配線材料として大きな注目を集めている[1]。我々は次世代CMOSチャネル候補としてのグラフェンの高いポテンシャルに着目し、グラフェン大面積基板上での成長技術やFET作製プロセス開発を行ってきた[2]。さらに、2009年の内閣府総合科学技術会議にて採択された最先端研究開発支援プログラム研究課題の一つ「グリーン・ナノエレクトロニクスのコア技術開発」を元に、グラフェンを用いた低消費電力デバイスの実現を目指しつくばの産総研を中心として研究開発を展開している。

これまで、従来は転写なしでは作製できなかったグラフェンFETをCVD合成後に転写なしで直接基板上に作製することに成功し、現在の半導体プロセスにより親和性の高い作製プロセスを提案した[2]。しかし、得られたグラフェンのデバイス特性は想定を大きく下回る結果となっており、現在の解決課題の一つとなっている。その理由として、CVD合成で得たグラフェンの低い結晶性やプロセス中に受けるダメージといった点が幾つか挙げられるが、最近、グラフェンと直接接触するゲート絶縁膜がグラフェンの特性に影響を及ぼしている可能性が示唆された[3]。

以前の実験(2011B1984)の結果、SiO2 薄膜や酸化Al薄膜がグラフェンの電子状態を大きく変えない絶縁膜であることがわかった[4]。しかし、実効酸化膜厚(EOT)の低下のためには、HfO2 や Al2O3 といった高誘電率絶縁膜の使用が望ましい。そこで、今回は、グラフェン上にバッファ層として SiO2 薄膜を堆積した上で熱ALD法及びプラズマALD法により絶縁膜を堆積し、絶縁膜の界面電子状態の観測することによりバッファ層である SiO2 薄膜上におけるALD法による絶縁膜の可否、すなわちゲート絶縁膜として適用に十分な堆積モードを有するかどうかの調査を行った。ゲート絶縁膜として機能させるために理想的な堆積モードは層状成長であり、まずはその確認を行うことが目的となる。得られた結果を元に最適なゲートスタック候補の選定が可能となり、グラフェンFET構造、作製プロセスの開発に大きく貢献することとなる。

実験:

実験はSPring-8、BL46XUで行い、入射光エネルギーは 7939 eV、アナライザーには SES-R4000 を用いた。また、Auのフェルミ端によりエネルギーの較正を行った。Pass Energyは 200 eV、光電子検出角は 80° を用い、測定は全て室温で実施した。測定した内殻準位は、Si 1s、Al 1s、Hf 3d、C 1s、O 1s である。測定した試料には熱酸化膜付Si基板上に 500 nm ないしは 1000 nm 堆積した銅上に熱CVD法により合成したグラフェンを用い、その上に電子ビーム蒸着法により、SiO2 薄膜を 0.5-5 nm 程度の異なる膜厚で堆積を行った。続けて、熱ALD法により、Al2O3 薄膜を 2、5、20 nm の異なる膜厚で堆積を行った。また、同じくプラズマALD法により、Al2O3 及び HfO2 薄膜をそれぞれ 1、5 nm 及び 1、5、10 nm と異なる膜厚で堆積を行った。

結果および考察:

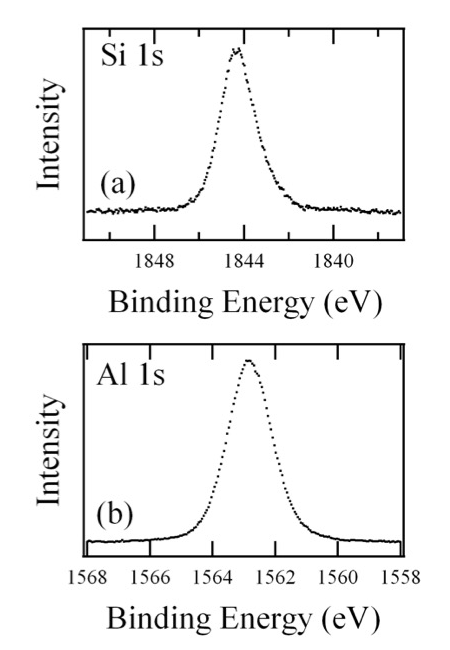

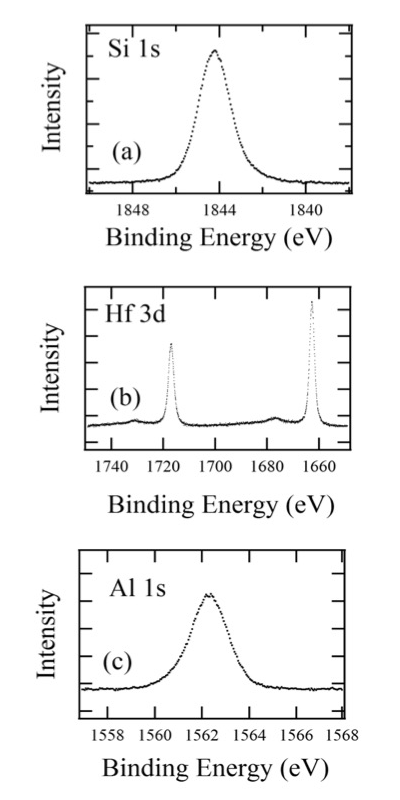

今回用いた熱ALD法及びプラズマALD法では水蒸気及び酸素プラズマを用いるためにグラフェンにダメージが及ぶ可能性が少なからずあるため、グラフェンと高誘電率絶縁膜の界面における SiO2 薄膜は絶縁膜堆積のためのテンプレートとしてだけでなくグラフェンの劣化防止の役割を担う。事前に行ったRaman分光と光電子分光実験の結果、SiO2 薄膜が 2 nm 以上であればALD法による影響がグラフェンに及ばないことを確認した。図1(a)及び(b)に、SiO2 薄膜をグラフェン上に 2 nm 蒸着した後に、Al2O3 薄膜を 5 nm 熱ALD法により堆積した後測定した光電子スペクトルを示す。それぞれのスペクトルは Si 1s 及び Al 1s 内殻光電子スペクトルである。Al 1s 内殻光電子スペクトルからは単一の Al2O3 由来のピークのみを観測し、O 1s 内殻光電子スペクトルの結果も合わせ、SiO2 薄膜上に酸化した Al2O3 が堆積していることが示唆され、SiO2 薄膜上に熱ALD法による絶縁膜堆積が可能であることがわかった。また、Si 1s 内殻準位スペクトルにおいてカーボンとの結合に由来する成分は観測されず単一の SiO2 由来のピークのみであることがわかり、ラマン分光の測定からも同様の結果であったことから、グラフェンの電子状態を変調するような結合状態を有さないことが示唆された。これは、SiO2 薄膜がグラフェンとALD薄膜との界面材料として適していることを意味している。加えて、Raman分光において欠陥等が SiO2 薄膜堆積により誘起されることがないことが明らかとなり、事前に得られていた結果[4]を確認した。

図1. (a) Si 1s 及び (b) Al 1s 光電子スペクトル。

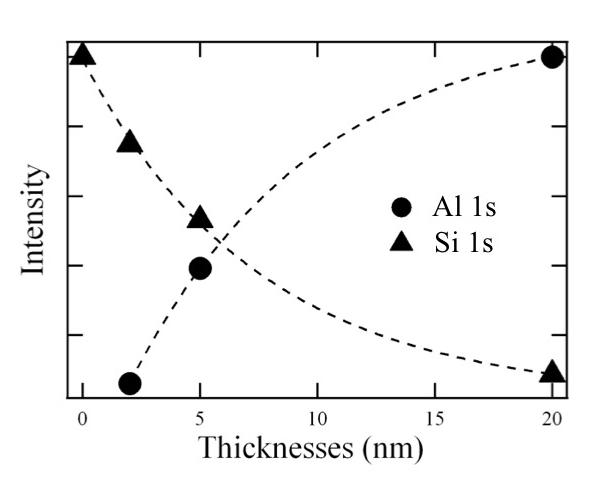

さらに、異なる Al2O3 膜厚から得られた Al 1s 及び Si 1s 内殻準位スペクトルの光電子強度を、堆積した絶縁膜の膜厚ごとにプロットしたのが次に示す図2である。Si 1s 及び Al 1s 内殻準位スペクトルの光電子強度は、それぞれ Al2O3 膜の堆積前と 20 nm 堆積した後に測定したスペクトルの光電子強度で規格化されている。Al 1s の光電子強度は Al2O3 薄膜の膜厚に応じて強度が exponential に増加しており、一方で下地となる Si 1s の光電子強度は exponential で減少している。この結果は、熱ALD法によりグラフェン上に SiO2 薄膜を介し Al2O3 薄膜が膜成長していることを意味している。また、下地となる SiO2 薄膜は Al2O3 薄膜の堆積中に拡散等は起こらず界面に安定して存在していることを示唆している。

図2. Al 1s 及び Si 1s 光電子ピーク強度の Al2O3 膜厚依存性。

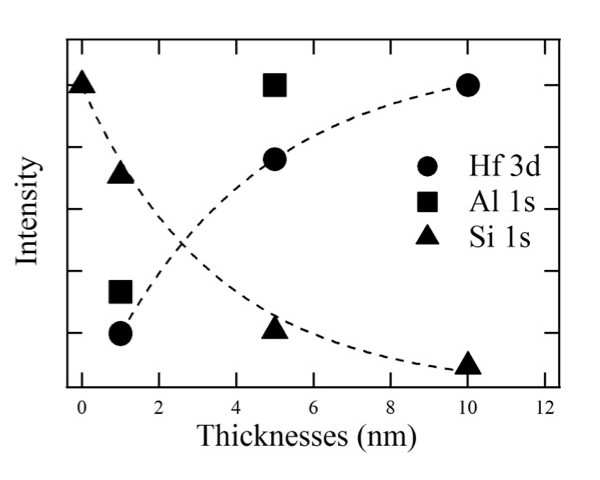

図3(a)及び(b)に、SiO2 薄膜をグラフェン上に 2 nm 蒸着した後に、熱ALDと同様にプラズマALD法により HfO2 薄膜 1 nm を堆積した後測定した光電子スペクトルを示す。それぞれのスペクトルはSi 1s、及び Hf 3d 内殻準位光電子スペクトルである。合わせて、図3(c)に SiO2 薄膜をグラフェン上に 2 nm 蒸着した後に、同じくプラズマALD法により Al2O3 薄膜 1 nm を堆積した後に測定した Al 1s 内殻光電子スペクトルを示す。熱ALD法の場合と同様に、SiO2 薄膜上に酸化した HfO2、及び Al2O3 が堆積していることが示唆され、SiO2 薄膜上にプラズマALD法による絶縁膜堆積が可能であることがわかった。また、Si 1s 内殻準位スペクトルにおいてカーボンとの結合に由来する成分は観測されず単一の SiO2 由来のピークのみであることがわかり、同じくグラフェンの電子状態を変調するような結合状態を有さないことが示唆された。熱ALDと同様にプラズマALD法で作製した HfO2 薄膜及び Al2O3 薄膜について得た Al 1s、Hf 3d 及びSi 1s 内殻準位スペクトルの光電子強度を堆積した絶縁膜の膜厚ごとにプロットしたのが次の図4である。 Si 1s、Hf 3d 及び Al 1s 内殻準位スペクトルの光電子強度は、それぞれプラズマALD法による堆積前、HfO2 薄膜 10 nm、及び Al2O3 薄膜 5 nm 堆積した後に測定したスペクトルの光電子強度で規格化されている。熱ALD法と同様に Hf 3d の光電子強度は HfO2 薄膜の膜厚に応じて強度が exponential に増加し、一方で下地となるSi 1s の光電子強度はexponentialで減少している。従って、プラズマALD法によっても、グラフェン上に SiO2 薄膜を介し HfO2 が膜成長していることを意味している。また、下地となる SiO2 薄膜は Al2O3 薄膜の堆積中に拡散等は起こらず界面に安定して存在していることを示唆している。なお、Al 1s の光電子強度についても、Hf 3d の光電子強度の振る舞いと同様の傾向を確認できるため、更なるデータ取得は必要であるものの Al2O3 薄膜は膜成長している可能性が示唆される。

図3. (a) Si 1s、(b) Hf 3d、及び(c) Al 1s 光電子スペクトル。

図4. Si 1s、Al 1s 及び Hf 3d 光電子ピーク強度の Al2O3 及び HfO2 膜厚依存性。

以上の結果から、熱ALD法及びプラズマALD法の何れの手法であっても、SiO2 と Al2O3 ないしは HfO2 の組み合わせがグラフェントランジスタのゲートスタックとし適用可能であることが明らかとなった。硬X線光電子分光では、二つの手法の差異は明らかにできなかったため、今後実際にゲート絶縁膜としてグラフェンデバイスに展開する中で検討を行っていく予定である。

まとめと今後の課題:

以上のように、ゲート絶縁膜候補材料とグラフェン界面での電子状態から、絶縁膜としての適性の有無の検討を行った。引き続き、光電子分光実験を継続するとともに、今後は絶縁膜の種類、及び蒸着や分子線エピタキシーを含むその他の堆積法の違いとグラフェンの電気特性の相関も調査し、グラフェントランジスタの最適なゲートスタック候補の選定を進めていく予定である。

参考文献:

[1] K. S. Novoselov et al., Science, 306, 666 (2004).

[2] D. Kondo et al., Appl. Phys. Express, 3, 025102 (2010).

[3] K. Kamiya et al, Phys. Rev. B, 83, 153413 (2011).

[4] 近藤 他、SPring-8/SACLA利用研究成果集, 3, 461 (2015).

ⒸJASRI

(Received: September 30, 2017; Accepted: December 17, 2018; Published: January 25, 2019)